# MOTOROLA MC6839 FLOATING POINT ROM

# TABLE OF CONTENTS

| Sectio |  |

|--------|--|

# Title

# SECTION 1. INTRODUCTION

| 1.1 | Early A | Approach 1 | to  | Mat | he | ma | t | ica | 1 | 0 | Der | rat | ti | DN |   |   | • |   | • | • | • |   | • |   | • | 1-1 |

|-----|---------|------------|-----|-----|----|----|---|-----|---|---|-----|-----|----|----|---|---|---|---|---|---|---|---|---|---|---|-----|

| 1.2 | Program | ns-in-ROM  |     | •   | •  | •  | • |     | • | • |     |     | •  | •  |   |   |   | • |   |   |   | • |   | • |   | 1-2 |

| 1.3 |         | Floating   |     |     |    |    |   |     |   |   |     |     |    |    |   |   |   |   |   |   |   |   |   |   |   |     |

|     | 1.3.1   | General    |     |     | •  |    |   |     |   | • |     |     |    |    |   |   |   |   |   |   |   |   |   |   |   | 1-2 |

|     | 1.3.2   | Pin Ass'   | ign | mer | t  |    | • |     |   |   | •   |     | •  |    | • | • | • |   |   |   |   |   |   |   |   | 1-3 |

#### SECTION 2. STANDARD FLOATING POINT FORMATS

| 2.1 | Introduction                                     |

|-----|--------------------------------------------------|

| 2.2 | Normalized Numbers                               |

|     | 2.2.1 Single Precision Format                    |

|     | 2.2.2 Double Precision Format                    |

|     | 2.2.3 Extended Format                            |

| 2.3 | Special Values (Single and Double Memory Format) |

|     | 2.3.1 Zero                                       |

|     | 2.3.2 Infinity                                   |

|     | 2.3.3 Small Numbers (Denormalized)               |

|     | 2.3.4 Not a Number (NAN)                         |

| 2.4 | Special Values (Extended Format)                 |

|     | 2.4.1 Zero                                       |

|     | 2.4.2 Infinity                                   |

|     | 2.4.3 Denormalized Numbers                       |

|     | 2.4.4 NANS                                       |

|     | 2.4.5 Unnormalized Numbers                       |

| 2.5 | BCD Strings                                      |

| 2.6 | Binary Integers                                  |

# SECTION 3. SUPPORTED OPERATIONS

| 3.1 | Introduction        | • | • | • | • | • | • | • | • | • | •  | • |   | • | • |   |   | • | • | • |   | • | •  | 3-1 |

|-----|---------------------|---|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|---|---|---|---|---|----|-----|

| 3.2 | Required Operations |   |   | • |   |   |   |   | • | • | •  | • |   |   | • |   |   |   | • | • | • | • | •. | 3-1 |

| 3.3 | Extra Operations    | • | • | • | • | • | • | • | • | • | 18 | • | • | • | • | • | • | • | • | • | • | ٠ | •  | 3-2 |

| 3.4 | Architecture        | • | • |   | • | • | • | • | • |   | •  |   |   |   | • | ٠ | • | • | • | ٠ | 9 | • | ٠  | 3-2 |

# SECTION 4. MODES OF OPERATION

| 4.1 | Introduction            |    | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 4-1 |

|-----|-------------------------|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| 4.2 | Rounding Modes          |    |   |   |   |   |   |   |   |   | • |   |   |   |   | • | • | • | • | 4-1 |

|     | 4.2.1 Rounding Precisio | n. |   |   |   |   |   |   |   |   |   |   |   |   |   |   | • |   |   | 4-1 |

|     | 4.2.2 No Double Roundin | g. |   |   |   |   |   | • |   |   | • | • |   | • |   | • | • | • | • | 4-2 |

# TABLE OF CONTENTS (Continued)

| Section | Title Pa               | ge |

|---------|------------------------|----|

| 4.3     | Infinity Closure Modes | -2 |

|         | 4.3.1 Affine Closure   | -2 |

| 4.4     | Exception Modes        |    |

#### SECTION 5. FLOATING POINT CONTROL BLOCK

| 5.1 | Introduction     |   |  |  |  |  |  |  |  |  |  |   |  |  |

|-----|------------------|---|--|--|--|--|--|--|--|--|--|---|--|--|

| 5.2 | Control Byte     | • |  |  |  |  |  |  |  |  |  | • |  |  |

| 5.3 | Status Byte      |   |  |  |  |  |  |  |  |  |  |   |  |  |

| 5.4 | Trap Enable Byte |   |  |  |  |  |  |  |  |  |  |   |  |  |

| 5.5 | Trap Vector      |   |  |  |  |  |  |  |  |  |  |   |  |  |

| 5.6 | Secondary Status |   |  |  |  |  |  |  |  |  |  |   |  |  |

# SECTION 6. USER INTERFACE

| 5.1 | Introduc | ction      |     |    |    |     |     |     |     |   |  |  |  |  |  |  |  |  |

|-----|----------|------------|-----|----|----|-----|-----|-----|-----|---|--|--|--|--|--|--|--|--|

| 5.2 | Operatio | on Opcode: | s a | nd | En | try | / F | Pot | int | s |  |  |  |  |  |  |  |  |

|     |          | quiremen   |     |    |    |     |     |     |     |   |  |  |  |  |  |  |  |  |

|     |          | Sequence   |     |    |    |     |     |     |     |   |  |  |  |  |  |  |  |  |

|     | 6.4.1    | Register   | Ca  | 11 |    |     |     |     |     |   |  |  |  |  |  |  |  |  |

|     | 6.4.2    | Stack Ca   | 11  |    |    |     |     |     |     |   |  |  |  |  |  |  |  |  |

## APPENDICES

A -- Operation Descriptions

(

- B -- Application Example of the Quadratic Equation

- C -- Detailed Description of Operations

- D -- Rounding and Exception Checking Routines

- E -- Program Details and Stack Frame Description

- F -- Internal Formats

- G -- Basic Levels of Precision

- H -- Definitions and Abbreviations

# SECTION 1 INTRODUCTION

# 1.1 EARLY APPROACH TO MATHEMATICAL OPERATION

Since the earliest days of computers, it has been obvious that no computer was capable of doing all the desired mathematical operations in binary integer arithmetic. Some early implementations perform floating point operations as a long string of BCD characters. Although the accuracy of this approach and the ease of implementation make it a popular alternative, the speed is too slow for most applications. Even though the BCD approach is still used today in most BASIC systems and in most systems doing dollars and cents calculations, most scientific calculations use a binary floating point representation.

As binary floating point became widely used during the 1960s, each computer manufacturer created his own floating point representation. There was (and is) a wide variation in formats and accuracy which almost guarantees that a program executed on one computer will get different results if executed on another computer. The mini-computer manufacturers improved the representations somewhat; but each manufacturer still had a different format and different ways to represent and handle exceptions and errors.

Meanwhile, research has been completed which formulates an optimal binary floating point representation. Unfortunately, the existing manufacturers had far too much money invested in software and hardware to incur the costs of conversion to a new standard. Powerful microprocessors, on the other hand, were in their infancy and the floating point invested in recognized the opportunity to standardize a floating point format for microprocessors. The IEEE appointed a committee to address the standard. This manual describes an implementation of a proposed IEEE standard, for the MC6809 Microprocessor (MPU), which is in a ROM. The information discussed in this manual is not a "restatement of the proposed IEEE standard," Instead, it addresses those areas that are required by the proposed IEEE standard and those optional areas that are implemented for the MC6809. Specific details of the proposed IEEE standard can be found in *IEEE Proposed Standard for Binary Floating Point Arithmetic Daft 8.0* (referred to as the proposed IEEE standard in this manual bits in the IEE.\*

Much of the Information, and many of the suggestions, for the proposed IEEE standard originated in a series of papers, published by Jerome Coonen at the University of California at Berkeley, the most recent of which is entitled "Specifications for a Proposed Standard for Floating Point Arithmetic" and appeared in the January 1980 issue of *Computer* magazine.

# 1.2 PROGRAMS-IN-ROM

From its inception, the MC6809 MPU was designed to support a concept of "ROMable" software by using an improved instruction set and addressing modes. One way, and to some extent the only way, to reduce the escalating cost of software was to supply "software on silicon." Since the original cost of developing the software can be amortized over a very large number of parts, the actual cost of the ROM part is low.

Shortly after completing the MC6809 MPU, Motorola selected floating point to become the first Motorola Standard Product ROM (SPR). Floating point was selected because it is standard software that can be used in many diverse systems. Furthermore, implementation of the proposed IEEE standard is sufficiently complex that many potential customers would not wish to develop the necessary expertise to write their own software; however, they would enjoy the advantages of its many benefits.

Hardware Implementations of floating point are always much faster (and more expensive) than software implementations. However, the MC6839 Floating Point ROM substitutes increased functionality for speed. In addition, the MC6839 Floating Point ROM supports all precisions, modes, and operations required or suggested by the proposed IEEE standard.

## 1.3 MC6839 FLOATING POINT (FP) ROM

#### 1.3.1 General

The MC6839 FP ROM provides floating point capability for the MC6809 and MC6809E MCUs. It implements the entire proposed IEEE standard providing a relatively simple, economical, and reliable solution to a wide variety of numerical applications. The MC6839 FP ROM provides three different formats, namely: single precision, double precision, and extended. Both the single and double precision formats provide results which are bit-for-bit reproducible across all proposed IEEE standard implementations. The extended format provides the extra precision needed for the intermediate results of long calculations, particularly the implementation of transcendental functions and interest calculations. All applications benefit from the extensive error checking and well-defined responses to exceptions, which are strengths of the proposed IEEE standard.

The MC6839 FP ROM takes full advantage of the advanced architectural features of the MC6809/MC6809E MPU. It is position independent and re-entrant, facilitating its use in real-time, multi-tasking systems.

This proposed standard was published in the April 1981 issue of Computer magazine.

A brief summary of the MC6839 FP ROM is shown below:

- Totally Position Independent

- · Operates in any Contiguous 8K Block of Memory

- · Re-Entrant

- . No Use of Absolute RAM

- All Memory References are made Relative to the Stack Pointer

- Flexible User Interface

- Operands are Passed to the FP Package by One of Two Methods 1) Machine Registers are Used as Pointers to the Operands 2) The Operands are Pushed onto the Hardware Stack

- The Latter Method Facilitates the Use of the MC6839 FP ROM in High-Level Language Implementations

.

- Easy to Use Two/Three Address Architecture

- The User Specifies Addresses of Operands and Result and Need Not be Concerned with any Internal Registers or Intermediate Results

- A Complete Implementation of the Proposed IEEE Standard

- Includes All Precisions, Modes, and Operations Required or Suggested by the Standard

- Includes the Following Operations:

Add Subtract Multiply Divide Remainder Square Root Integer Part Absolute Value Negate Predicate Compares Condition Code Compares Convert Integer – Floating Point Convert Binary Floating Point – Decimal String

#### 1.3.2 Pin Assignment

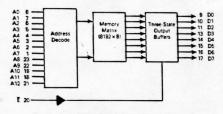

The MC6639 FP ROM is housed in one 24-pin 8K-by-8 mask programmable ROM: the MCM68364. It uses a single 5 V power supply and is available with access times of 250 or 350 ns. For electrical characteristics, refer to the Advance Information Sheet for the MC68A39 (1.5 MHz) and MC68B39 (2.0 MHz).

Figure 1-1 shows a pin assignment diagram of the MC6839 FP ROM and Figure 1-2 contains a block diagram of the device.

5

1º

5

ę

Figure 1-2. MC6839 FP ROM Block Diagram

# SECTION 2 STANDARD FLOATING POINT FORMATS

# 2.1 INTRODUCTION

The MC6839 Floating Point ROM (also referred to as the floating point package in this manual) supports three precisions of floating point numbers: single, double, and extended. It supports normalized numbers plus four special types of numbers for each precision: zeros, infinities, NANs, and denormalized numbers. The following paragraphs described how the numbers are represented in user memory for each precision. Also described are the formats used to represent binary integers and BCD strings.

#### 2.2 NORMALIZED NUMBERS

Normalized numbers are floating point numbers that are not one of the special types. The bulk of the numbers in any real program will be normalized numbers. Three different formats are used with normalized numbers, namely: single precision format, double precision format, and extended format.

## 2.2.1 Single Precision Format

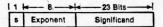

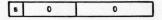

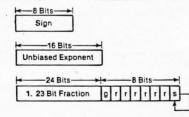

All single precision numbers are represented in a four byte string as shown below:

In single precision formats shown above, the exponent is blased by + 127. That is, an exponent of: 0 is 127, 2 is 129, and -2 is 125.\* A normalized floating point number always has a 1 to the left of the binary point; this bit is not explicit in the memory formats. This saves one bit in memory which allows more precision with the same number of bits. In this specification, the fraction is referred to as a significand in order to indicate that it has an implied 1.0 added to the fraction. Hence, significands lie in the range

<sup>\*</sup>A biased exponent makes floating point compare easier to implement since the exponent and significant can be considered as a long integer. Also, an unsigned integer compare can be used to calculate the condition codes rather than a floating subtract.

1.0< significand</p>

2.0. S is the sign of the significand. The significand is stored in sign magnitude rather than twos complement form. The equation for the single precision format representation is:

$X = (-1)^2 \times 2(exponent - 127) \times (1.significand).$

= sign bit = bit string length of 1.

- exponent = biased exponent bit string length of 8.

- significand = bit string length of 23 encoding the significant bits of the number that low the binary point, yielding a 24 bit significand digit field for the number that always begins "1\_\_\_".

Examples:

.

- + 1.0 = 1.0 × 20 = \$3F, 80, 00, 00

- + 3.0 = 1.5 × 21 = \$40, 40, 00, 00

- -1.0 = -1.0 × 20 = \$BF, 80, 00, 00

- +7.0 = 1.75 × 22 = 140, E0, 00, 00

- + 0.5 = 1.0 × 2 1 = \$3F, 00, 00, 00

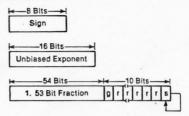

#### 2.2.2 Double Precision Format

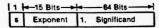

All double precision numbers are represented in an eight byte string as shown below:

| 111 | -11 Bits- | 52 Bits     |

|-----|-----------|-------------|

| 5   | Exponent  | Significand |

In the double precision format shown above, the exponent is blased by + 1023. Interpretation of the format is similar to the single precision format except the bias is + 1023 instead of + 127. The equation for the double precision format representation is:

X=(-1)<sup>5</sup> x s(exponent - 1023) x (1.significand)

Examples:

7.0 =  $1.75 \times 2^2 =$ \$40, 1C, 00, 00, 00, 00, 00, 00 16.0 =  $1.0 \times 2^4 =$ \$40, 30, 00, 00, 00, 00, 00, 00 30.0 =  $1.875 \times 2^4 =$ \$40, 3E, 00, 00, 00, 00, 00, 00  $-30.0 = -1.875 \times 2^4 =$ \$40, 3E, 00, 00, 00, 00, 00, 00  $0.25 = 1.0 \times 2^{-2} =$ \$3F, D0, 00, 00, 00, 00, 00

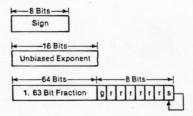

#### 2.2.3 Extended Format

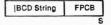

Single and double precision formats should be used to represent the majority of floating point numbers in the user's system (e.g., storage of arrays). The extended format should only be used for intermediate calculations such as occur in the evaluation of a complex expression. In fact, extended format may never be required by most users; however, since it is required internally, it is optionally provided. Extended numbers are represented in a 10 byte string as shown below:

A notable difference between this format and the single and double precision formats is that the 1.0 is explicitly present in the significand and the exponent contains no bias and is in twos complement form. The equation for double extended is:

X = (-1)S x 2(exponent) x significand

Where the significand contains the explicit 1.0.

Examples:

$\begin{array}{l} 30.0 = 1.875 \times 2^4 = \$00, \ 04, \ F0, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 00, \ 0$

#### 2.3 SPECIAL VALUES (SINGLE AND DOUBLE MEMORY FORMAT)

No derivable floating point format can represent the infinite number of possible real numbers, so it is very useful if some special numbers are recognized by a floating point package. These numbers are: +0, -0, + infinity, -Infinity, very small (almost zero) numbers, and in some cases unnormalized numbers. It is also convenient to have a special format to indicate that the contents of memory do not contain a valia floating point number. This "not a number" might occur if a variable is defined in a high level language (HLL) and is used before it is initialized with a value. The most positive and negative exponents of each format are reserved to represent these special values. How these special format numbers enter into calculations will be covered in the detailed description of each operation (Appendix C).

## 2.3.1 Zero

Zero is represented by a number with both a zero exponent and a zero significand. The sign is significant and differentiates between plus or minus zero.

#### 2.3.2 Infinity

The infinities are represented by a number with the maximum exponent and a zero significand. The sign differentiates plus or minus infinity.

# 2.3.3 Small Numbers (Denormalized)

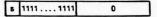

When a number is so small that its exponent is the smallest allowable normal blased value (1), and it is impossible to normalize the number without further decrementing the exponent, then the number becomes denormalized. The formal for denormalized numbers has a zero exponent and a nonzero significand. Note that in this form the implicit bit is no longer one but is zero. The interpretation for denormalized numbers is:

Single:  $X = (-1)^5 \times 2^{-126} \times (0. significand)$

Double:  $X = (-1)^5 \times 2 - 126 \times (0. significand)$

Note that the exponent is always interpreted as 2-126 for single and 2-1022 for double instead of 2-127 and 2-1023 as might be expected. This is necessary since the only way to insure that the implicit bit becomes zero is to right shift the significant (divide by 2) and increment the exponent (multiply by 2). Thus the exponent ends up with the interpretation of 2-126 or 2-1022.

The format for denormalized numbers is:

Note that zero may be considered a special case of denormalized numbers where the number is so small that the significand has been reduced to zero. The concept of denormalized numbers has perhaps been the most controversial aspect of the proposed IEEE standard. However, the concept of allowing a number to "gently underflow" to zero seems intuitive and straightforward to most inexperienced users who do not have a builtin bias for some existing floating pionir representation.

Examples:

Single:  $1.0 \times 2 - 128 = 0.25 \times 2 - 126 = 00, 20, 00, 00$ Double:  $1.0 \times 2 - 1025 = 0.125 \times 2 - 1022 = 00, 02, 00, 00, 00, 00, 00, 00$

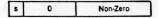

#### 2.3.4 Not a Number (NAN)

The format for NANs has the largest allowable exponent, a nonzero significand, and an undefined sign. As an implementation feature (not IEEE required), the nonzero fraction and undefined sign are further defined as shown below:

| 0 | 1111 1111 | t | Operation Address | 00000 |

|---|-----------|---|-------------------|-------|

|---|-----------|---|-------------------|-------|

d: 0 = This NAN has never entered into an operation with another NAN.

1 = This NAN has entered into an operation with other NANs.

t:0=This NAN will not necessarily cause an invalid operation trap when operated upon.

1 = This NAN will cause an invalid operation trap when operated upon (trapping NAN). Operation address:

The 16 bits immediately to the right of the t bit contain the address of the instruction immediately following the call to the floating point package of the operation that caused the NAN to be created. If d (double NAN) is also set, the address is arbitrarily one of the addresses in the two or more participating NANs.

# 2.4 SPECIAL VALUES (EXTENDED FORMAT)

The special values discussed below are implemented using the extended format which was discussed earlier in this section. As explained before, numbers are represented in this format as a 10 byte string.

# 2.4.1 Zero

Zero is represented by a number with the smallest unbiased exponent and a zero significand:

# 2.4.2 Infinity

Infinity has the maximum unbiased exponent and a zero significand:

|   | -15 Bits  | -64 Bits |

|---|-----------|----------|

| 8 | 011111 11 | 0        |

## 2.4.3 Denormalized Numbers

Denormalized numbers have the smallest unbiased exponent and a nonzero significand:

| 1 | -15 Bits | -64 Bits |

|---|----------|----------|

| 5 | 100 000  | Nonzero  |

The exponent of denormalized extended and internal numbers is - 16384, and has the value:

(-1)\$ x2-16383 x0.1

Example:

1.0 × 2 - 16387 × 0.125 × 2 - 16384 × 40, 00, 08, 00, 00, 00, 00, 00, 00, 00

### 2.4.4 NANS

These have the largest unbiased exponent and a nonzero significand. The operation addresses, "t" and "d", are implementation features and were defined in an earlier paragraph of this section.

|   |          |   |   | H 16 Bits         |          |

|---|----------|---|---|-------------------|----------|

| d | 011 1111 | 0 | 1 | Operation Address | 00000000 |

The operation address always appears in the 16 bits immediately to the right of the t bit.

## 2.4.5 Unnormalized Numbers

C

Unnormalized numbers occur only in extended or internal format. Unnormalized numbers have an exponent which is greater than the minimum established for the extended format (i.e., they are not denormalized or normal zero); however, the explicit leading significand bit is a zero. If the significand is zero, this is an unnormalized zero. Even though unnormalized and denormalized numbers are handled similarly in most cases, they should not be confused. Denormalized numbers are numbers that are very small (have minimum exponent) and hence have lost some bits of the significance. Unnormalized numbers are not necessarily small (the exponent may be large or small) but the significand has lost some bits of significance, hence, the explicit bit and possibly some of the bits to the right of the explicit bit are zero.

Unnormalized numbers cannot be represented (thus, cannot represent a result) for single precision and double precision formats. Unnormalized numbers can only be created when denormalized numbers, in single precision or double precision formats, are converted to extended (or internal) formats.

Example:

$0.0625 \times 2^2$  (unnormalized) = 00, 02, 08, 00, 00, 00, 00, 00, 00, 00

## 2.5 BCD STRINGS

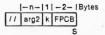

A BCD string is the input to the BCD-to-FP operation and the output of the FP-to-BCD operation. All BCD strings are represented by a 26 byte string with the following format:

| 0  |                      | 5  | 6 24                  | 25 | (Byte #) |

|----|----------------------|----|-----------------------|----|----------|

| se | 4 Digit BCD Exponent | sf | 19 Digit BCD Fraction | P  |          |

se = sign of the exponent.  $00_{16}$  = plus, OF<sub>16</sub> = minus. (1 byte) sf = sign of the fraction.  $00_{16}$  = plus, OF<sub>16</sub> = minus. (1 byte) p = number of fraction digits to the right of the decimal point. (1 byte)

All BCD digits are unpacked and right justified in each byte:

The byte ordering of the fraction and exponent is consistent with all Motorola processors in that the most significant BCD digit is in the lowest memory address.

#### 2.6 BINARY INTEGERS

Two sizes of binary integers are supported: short and double. Short integers are 16 bits long and double integers are 32 bits long. The byte ordering is consistent with all Motorola processors in that the most significant bits are in the lowest address.

# SECTION 3 SUPPORTED OPERATIONS

#### **3.1 INTRODUCTION**

The supported operations are divided into two groups: those required by the proposed IEEE standard, and those implemented to support real data types for Motorola Pascal. A larger number of operations are required by the proposed standard to insure portability of floating point algorithms.

# **3.2 REQUIRED OPERATIONS**

The operations required to support the proposed IEEE standard are shown in Table 3-1. The mnemonic column in Table 3-1 illustrates the suggested mnemonics although, at present, no Motorola assembler supports them. The opcodes are used when calling the MC6839 to differentiate the various functions. The method for calling is described in Section 6.

All routines shown in Table 3-1, except FMOV and the compares (FCMP, FTCMP, FPCMP, and FTPCMP), accept arguments of the same precision and generate a result containing the same precision.

| Opcode | Mnemonic | Operation                                                     |

|--------|----------|---------------------------------------------------------------|

| 00     | FADD     | arg1 + arg2- result                                           |

| 02     | FSUB     | arg1-arg2-result                                              |

| 04     | FMUL     | arg1 x arg2-result                                            |

| 06     | FDIV     | arg1/arg2-result                                              |

| 08     | FREM     | remainder (arg1/arg2i-result                                  |

| BA     | FCMP     | arg1 - arg2, set condition codes                              |

| CC     | FTCMP    | arg1 - arg2, set condition codes, trap on unordered           |

| BE     | FPCMP    | arg1-arg2, affirm or disaffirm a predicate                    |

| DO     | FTPCMP   | arg1-arg2, affirm or disaffirm a predicate, trap on unordered |

| SA     | FMDV     | move (or convert) arg2-result                                 |

| 12     | FSORT    | square root arg2-result                                       |

| 14     | FINT     | integer part of arg2-result                                   |

| 16     | FFIXS    | floating arg2-short integer result                            |

| 18     | FFIXD    | floating arg2-double integer result                           |

| 24     | FFLTS    | short integer arg2-floating result                            |

| 26     | FFLTD    | double integer arg2-floating result                           |

| 10     | BINDEC   | binary floating-decimal BCD string                            |

| 22     | DECBIN   | decimal BCD string-binary floating                            |

| Table 3-1. | Required | Operations to Su | pport IEEE Standard |

|------------|----------|------------------|---------------------|

|------------|----------|------------------|---------------------|

# **3.3 EXTRA OPERATIONS**

In order to support Motorola Pascal, two other operations are supplied. They include:

| Opcode | Mnemonic | Operation                       |

|--------|----------|---------------------------------|

| 1E     | FAB      | Absolute Value of arg2 - Result |

| 20     | FNEG     | -arg2 - Result                  |

# 3.4 ARCHITECTURE

All floating point operations are of the "two address" or "three address" variety; all the user need supply are the addresses of both the operand(s) and the result. The package looks for operands at the specified location(s) and delivers the result to the specified destination. For example,

> arg1 + arg2 - Result <Source> + <Source> - <Destination>

The only permanent state information is contained in floating point control block (FPCB) which defines the modes of the package. This control block is much like the control blocks frequently used to define I/O or operating system operations. The FPCB is discussed in detail in Section 5.

# SECTION 4 MODES OF OPERATION

# 4.1 INTRODUCTION

In addition to supporting a wide range of precisions and operations, the MC6839 Floating Point ROM supports all modes required or suggested by the proposed IEEE standard. These include: rounding modes, infinity closure modes, and exception handling modes. The various modes are selected by bits in the floating point control block (FPCB) that resides in user memory. Thus, a unique set of modes is available for user calculations. The selection bits in the FPCB are defined in Section 5 of this manual. Details of algorithms used for rounding and exception checking are discussed in Appendix C.

For most users, the default modes specified in the proposed IEEE standard will be sufficient. The strength of the proposed IEEE standard is that it provides experienced numerical analysts with the necessary tools (modes) to generate special complex programs while, at the same time, making it easier for the average engineering user to get the best results possible by selecting the defaults.

#### 4.2 ROUNDING MODES

For the following examples, assume z is the infinitely precise result of an arithmetic operation. Further, assume z1 and z2 are the nearest numbers that bracket z and can be exactly represented in the selected precision. That is: z1<z<z2 (barely). Then the following criteria are used to select the delivered result.

Round to Nearest (RN) — The nearer of z1 or z2 is selected. In the case of a tie, either of z1 or z2 with a zero, least significant bit is chosen (round to even). This is the default mode.

Round Toward Zero (RZ) — The smaller in magnitude of z1 and z2 is selected (truncation).

Round Toward Plus Infinity (RP) - z2 is selected.

Round Toward Minus Infinity (RM) - z1 is selected.

## 4.2.1 Rounding Precision

Normally a result is rounded to the precision of its destination. However, when the destination is Extended Format, the user may specify that the result significand be rounded to the precision of the basic format of his choice, although the exponent range remains extended. This allows programs written for an implementation with only the smaller basic formats to be moved to a full implementation and still generate the same results.

#### 4.2.2 No Double Rounding

The MC6839 Floating Point ROM is implemented such that no result will undergo more than one rounding error.

#### 4.3 INFINITY CLOSURE MODES

The way in which infinity is handled in a floating point package may limit the number of applications in which the package can be used. To solve this problem, the proposed IEEE standard requires two types of infinity closures. A bit in the control byte of the floating point control block (FPCB) will select the type of closure that is in effect at any time.

## 4.3.1 Affine Closure

In affine closure: minus infinity < (every finite number) < plus infinity. Thus infinity takes part in the real number system in the same manner as any other signed quantity. The sign of zero also takes on meaning in affine mode such that:

+ n/+0 = plus infinity > + n/-0 = minus infinity where n = floating point number.In all other operations, +0 and -0 participate identically.

#### 4.3.2 Projective Closure

In projective closure: infinity = minus infinity = plus infinity, and all comparisons between infinity and a real number involving order relations other than equal ( $\pm$ ) or not equal ( $\pm$ ) are invalid operations. In projective closure, the real number system can be thought of as a circle with zero at the top and infinity at the bottom. Thus, infinity + infinity and infinity – infinity are invalid operations. Projective closure is the default closure.

#### **4.4 EXCEPTION MODES**

Existing floating point implementations vary in the way they handle exceptions, so the proposed IEEE standard carefully prescribes how exceptions must be handled and what constitutes an exception. Seven types of exceptions will be recoprized by the MC6839 Floating Point ROM; however, only the first five are required by the proposed IEEE standard. These include:

- 1. Invalid Operation

- 2. Underflow

- 3. Overflow

- 4. Division by Zero

- 5. Inexact Result

- 6. Integer Overflow on FINT

- 7. Comparison of Unordered Values

For each exception the caller will have the option of specifying whether: (1) the routine should trap to a user supplied trap routine on exception or (2) deliver a default specified by the proposed standard and proceed with execution. In either case, a status bit is set in the FPCB status byte and remains set until cleared by the caller's program. The selection of whether to trap or continue is made by setting bits in the enable byte of the FPCB. For more details on the FPCB, see Section 5. For a detailed description of each exception, refer to Appendix D.

If a trap is taken, the floating point package supplies a pointer in the U register that points to the current stack frame (refer to Appendix D). This stack frame contains the following diagnostic information:

1. Which Event Caused the Trap (Overflow, etc.)

2. Its Location in the Caller's Program

- 3. The Opcode

- 4. The input Operands

- 5. The Default Result in Internal Format

In the event more than one exception occurs, only one trap will be invoked according to the following precedence:

- 1. Invalid Operation

- 2. Overflow

- 3. Underflow

- 4. Division by Zero

- 5. Unordered

- 6. Integer Overflow

- 7. Inexact Result

The user supplied trap routine (if any) will usually accomplish one of the four items listed below.

- Change the result on the internal stack to the desired result. This result can then be returned to the caller by the floating point package during its stack cleanup.

- Correct the result directly in the memory space of the caller. In this case the floating point package does not overwrite the result during its stack cleanup.

- Do nothing to the result and allow the floating point package to deliver the default value to the result.

- 4. Abort execution.

All user supplied trap routines must return to the floating point package (using an RTS instruction) for cleanup unless they abort. If the C-bit in the condition code register is set on return, then the result (possibly corrected by the trap) is returned to the destination; otherwise, no result is returned to the destination (with the assumption that the user supplied trap handler already returned a value to the destination).

# SECTION 5 FLOATING POINT CONTROL BLOCK

# **5.1 INTRODUCTION**

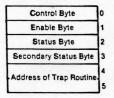

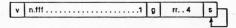

The floating point control block (FPCB) is a user defined block that contains information needed to select the operating mode for a particular call to the floating point (FP) package. The FPCB must be defined in user RAM. The FPCB is also used to pass status back to the caller or to invoke the trap routine. The caller of the floating point package must pass the address of the FPCB on each call (see Section 6, User Interface, for calling sequence details). The general form of the FPCB is:

The following paragrpahs discuss the use of the various bytes in the FPCB.

#### 5.2 CONTROL BYTE

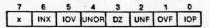

The control byte configures the floating point package for the caller's operation and is written by the user.

| 7 | 6         | 5 | 4 | 3   | 2     | 1    | 0   |

|---|-----------|---|---|-----|-------|------|-----|

| f | Precision |   | x | NRM | Round | Mode | AJP |

- Bit 0 Closure Bit 0 = Projective Closure 1 = Affine Closure

- Bits 1-2 Rounding Mode

- 00 = Round to Nearest (RN)

- 01 = Round Toward Zero (RZ)

- 10 = Round Toward Plus Infinity (RP)

- 11 = Round Toward Minus Infinity (RM)

Bit 3 Normalize Bit

1 = Normalize denormalized numbers while in internal format before using. Precludes the creation of unnormalized numbers.

0 = Do not normalize denormalized numbers (warning mode).

- Bit 4 Undefined, Reserved

- Bits 5-7 Precision Mode

- 000 = Single

001 = Double

010 = Extended With No Forced Rounding of Result

011 = Extended Force Round Result to Single

100 = Extended Force Round Result to Double

101 = Undefined, Reserved

110 = Undefined, Reserved

111 = Undefined, Reserved

For move and compare operations, bits 5-7 are "don't cares" since the source and destination precisions are specified by an extra argument passed to the routine. See Section 6, User Interface, for more details of the moves and compare.

Note that if the control byte is set to zero by the user, all defaults in the proposed IEEE standard will be selected.

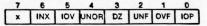

## 5.3 STATUS BYTE

The bits in the status byte are set by the MC6839 if any errors have occurred. Note that each bit of the status byte is a "sticky" bit and must be manually reset (written) by the user. The floating point package writes bits into the status byte but never clears existing bits. This is done so that a long calculation can be completed and the status need only be checked once at the end.

Bit 0 Invalid Operation (also see Secondary Status)

- Bit 1 Overflow

- Bit 2 Underflow

- Bit 3 Division by Zero

- Bit 4 Unordered

- Bit 5 Integer Overflow

- Bit 6 Inexact Result

- Bit 7 Undefined, Reserved

# 5.4 TRAP ENABLE BYTE

If any bit of the trap enable byte is set, it enables the floating point package to trap if that error occurs. The bit position definitions are the same as for the status byte. Note that if a trapping compare is executed and the result is unordered, then the unordered trap will be taken regardless of the state of the UNOR bit in the trap enable byte.

- Bit 0 Invalid Operation

- Bit 1 Overflow

- Bit 2 Underflow

- Bit 3 Division by Zero

- Bit 4 Unordered

- Bit 5 Integer Overflow

- Bit 6 Inexact Result

- Bit 7 Undefined, Reserved

# 5.5 TRAP VECTOR

If a trap occurs, the floating point package will initiate a jump indirectly through the trap address in the FPCB. An index in the A accumulator then indicates the trap type. Trap types are as follows:

- 0 = Invalid Operation

- 1 = Overflow

- 2 = Underflow

- 3 = Divide by Zero

- 4 = Unnormalized

- 5 = Integer Overflow

- 6 = Inexact Result

If more than one enabled trap occurs, the MC6839 Floating Point ROM returns the index of the highest priority enabled error. Index 0, which is an invalid operation, is the highest priority, whereas, index 6 (inexact result) is the lowest.

## 5.6 SECONDARY STATUS

The floating point package writes a status into this byte whenever a new IOP occurs. As is the case with the status byte, it is up to the caller to reset the "IOP type" field.

Bits 0-4 represent the invalid operation type field. These four bits are encoded as shown below.

0 = No IOP error

6

- 1 = Square Root of: a Negative Number, Infinity in Projective Mode, or a Not Normalized Number

- 2 = (+ Infinity) + (- Infinity) in Affine mode

- 3=Tried to Convert a NAN to Binary Integer

- 4 = In Division: 0/0, Infinity/Infinity, or the Divisor is not Normalized and the Dividend is Not Zero and is Finite

- 5= One of the Input Arguments was a Trapping NAN

- 6 = Unordered Values Compared via Predicate Other Than = or #

- 7 = k Out of Range for BINDEC or

- p Out of Range or DECBIN

- B = Projective Closure Use of +/- Infinity in Add or Subtract

- $9 = 0 \times Infinity$

- 10 = In Remainder arg2 is Zero, or Not Normalized in arg1 is Infinite

- 11 = Unused, Reserved

- 12 = Unused, Reserved

- 13 = Unused, Reserved

- 14 = Unused, Reserved

- 15 = Tried to MOV a Single Denormalized Number to a Double Destination

- 16 = Tried to Return an Unnormalized Number to Single or Double (also called Invalid Result in the Proposed IEEE Standard).

- 17-31 = Unused, Reserved

# SECTION 6 USER INTERFACE

#### 6.1 INTRODUCTION

There are two types of calls to the floating point package: register calls and stack calls. For register calls, the user loads the machine register with pointers (addresses) to the operand(s) and to the result; the call to the floating point package is then performed. For stack calls, the operand(s) is pushed onto the stack and the call to the floating point package is performed. The result then replaces the operands on the stack after completion. The operand(s) must be pushed least significant bytes first; this is consistent with the other Motorola architectures in that the most significant byte resides in the lowest address. The two types of calls look like:

General form of a register call:

load registers LBSR FPREG register call FCB opcode General form of a stack call: push arguments LBSR FPSTAK stack call FCB opcode pull result

## 6.2 OPERATION OPCODES AND ENTRY POINTS

The suggested mnemonics and the opcode values for the various operations available in this floating point package are shown below (in opcode order).

|          | Opcode | Operation                       |

|----------|--------|---------------------------------|

| Mnemonic | Value  | Description                     |

| FADD     | 00     | Add                             |

| FSUB     | 02     | Subtract                        |

| FMUL     | 04     | Multiply                        |

| FDIV     | 06     | Divide                          |

| FREM     | 08     | Remainder                       |

| FSQRT    | 12     | Square Root                     |

| FINT     | 14     | Integer Part                    |

| FFIXS    | 16     | Float - Short Integer           |

| FFIXD    | 18     | Float - Double Integer          |

| BINDEC   | 10     | Binary Float - BCD String       |

| FAB      | 1E     | Absolute Value                  |

| FNEG     | 20     | Nepate                          |

| DECBIN   | 22     | BCD String - Binary Float       |

| FFLTS    | 24     | Short Integer - Float           |

| FFLTD    | 26     | Double Integer - Float          |

| FCMP     | BA     | Compare                         |

| FPCMP    | BE     | Predicate Compare               |

| FMOV     | 9A     | Move (or Convert) arg1 - Result |

| FTCMP    | CC     | Trapping Compare                |

| FTPCMP   | DO     | Trapping Predicate Compare      |

The two entry points to the MC6839 are referred to as FPREG (register call) and FPSTAK (stack call). Their addresses are:

FPREG = ROM starting address + \$3D

FPSTAK = ROM starting address + \$3F

The first \$3C locations of the ROM contain a fixed size ROM header. The entry points for the floating package are located in a branch table immediately following this header. Therefore, the addresses of the entry points will remain constant for future versions of the ROM.

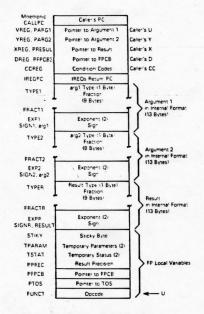

# 6.3 STACK REQUIREMENTS

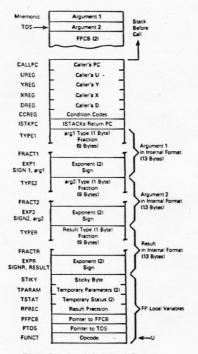

When the MC6839 Floating Point ROM is called by the user, local storage is reserved on the hardware stack by the floating point package. The input arguments are then moved from user memory to the local storage area, and are expanded into a convenient internal format. The operations use these "internal" numbers to arrive at an "internal" result. The internal" result is then converted to the memory format of the result and returned (as the result) to the user. For this reason, the user must insure that adequate memory exists on the hardware stack before calling the MC6839 Floating Point ROM. The maximum stack sizes that any particular operation will ever require are:

register calls 170 bytes stack calls 200 bytes

#### 6.4 CALLING SEQUENCE

#### 6.4.1 Register Call

In this calling method the addresses of the arguments and the floating point control block (FPCB) are passed in the register:

U = address of argument 1 Y = address or argument 2

X = address of result

D = address of FPCB

If an argument is not used in a particular operation, it need not be included. In monadic operations, Y contains the address of the single argument. The result may be the same address as either of the arguments. All registers will be restored on exit. Example of a position independent call to the add routine:

| LEAU | arg1, PCR    |                  |

|------|--------------|------------------|

| LEAY | arg2, PCR    |                  |

| LEAX | FPCBPTR, PCR | pointer to FPCB* |

| TFR  | X, D         |                  |

| LEAX | result, PCR  |                  |

| LBSR | foreg        |                  |

| FCB  | FADD         |                  |

Example of a position independent monadic call to the square root routine:

| LEAY | arg2, PCR    |

|------|--------------|

| LEAX | FPCBPTR, PCR |

| TFR  | X, D         |

| LEAX | result, PCR  |

| LBSR | FPREG        |

| FCB  | FSQRT        |

For some operations the arguments have slightly different meanings. See Appendix A for details. All subroutines in the floating point package are re-entrant and position independent. However, the caller must use caution to insure that his call does not violate the rules of re-entrancy or position independence. For example, each calling task should have its own FPCB to remain re-entrant. Also, if in the previous examples load immediates had been used, rather than load effective address program counter relative, the calling program could not have been position independent.

# 6.4.2 Stack Call

In this mode the actual argument(s), not their addresses, and the address of the FPCB are assumed to be on the top of the hardware stack and they will be removed and replaced by the result on exit. If two arguments are on the stack, then argument 2 should be above (lower address) argument 1. The address of the FPCB is on the top of the stack above the argument(s).

Example of a stack call to the add routine:

push argument 1 push argument 2 push FPCBPTR Pointer to FPCB LBSR FPSTAK FCB FADD pull result

For monadic operations, arg2 contains the single input argument and there is no arg1. On return, the FPCB pointer and any other parameters are lost from the top of the stack. The only object left on the stack after an operation is the result. For some operations, the arguments have slightly different meaning. See Appendix A for details.

<sup>&</sup>quot;Two instructions are required here if the caller wishes his call to remain position independent (there is no LEAD instruction).

# APPENDIX A OPERATION DESCRIPTIONS

# A.1 INTRODUCTION

This appendix contains detailed information covering specific operations and their required calling sequences. The operations are arranged in alphabetical order with a summary listing on the last page of this appendix. Detailed descriptions of the algorithms are provided in Appendix B.

#### A.2 NOTATION

6

In describing each specific operation, symbols are used to indicate the operation. Table A-1 lists these symbols and their meaning. Abbreviations which are used for the source form, various registers, bits, bytes, etc. are listed in Table A-2.

| Symbol | Meaning                      |  |  |

|--------|------------------------------|--|--|

| -      | Is Transferred As IStored As |  |  |

| •      | Boolean Exclusive DR         |  |  |

| + \    | Arithmetic Plus              |  |  |

| -      | Arithmetic Minus             |  |  |

| ×      | Arithmetic Multiply          |  |  |

## Table A-1. Specific Operation Notation

| Abbreviation | Meening                                                                                                  |

|--------------|----------------------------------------------------------------------------------------------------------|

| erg .        | Argument                                                                                                 |

| BCS          | Branch if Carry Set                                                                                      |

| BGE          | Branch if Greater Than or Equal to Zero                                                                  |

| BINDEC       | Binary Floating Point to Decimal String                                                                  |

| *DECBIN      | Decimal String to Binary Floating Point                                                                  |

| *FAB         | Absolute Value of an Argument                                                                            |

| *FADD        | Add                                                                                                      |

| FCB          | Form Constant Byte (assemble: directive)                                                                 |

| *FCMP        | Compare Compares two arguments and sets condition codes                                                  |

| *FDIV        | Divide Divides one argument by another                                                                   |

| *FFIXD       | Fix Double converts an argument from a floating point number into a 32-bit binary integer                |

| *FFIXS       | Fix Single converts an argument from a floating point number into a 16-bit binary mieger                 |

| *FFLTD       | Float Double converts a 32-bit brany integer into a floating point result                                |

| *FFLTS       | Float Single converts a 16-bn binary integer into a floating point result                                |

| *FINT        | Integer Part Fisating point argument is converted to as floating point integer part                      |

| *FMOV        | Move Moves an argument to the result (with any implied conversions)                                      |

| *FMUL        | Muhipiy Muhipies two arguments and stores the result.                                                    |

| *FNEG        | Negate Change the sign of an argument                                                                    |

| FPCB         | Floating Point Control Block                                                                             |

| *FPCMP       | Predicate Compare Compares two arguments and affirms or disaffirms a predicate                           |

| FPREG        | Register Call Entry Point                                                                                |

| FPSTAK       | Stack Call Entry Point                                                                                   |

| *FSORT       | Square Root Stores the square root of an argument                                                        |

| *FSUB        | Subtract '                                                                                               |

| *FTCMP       | Trapping Compare Compares two arguments and sets condition codes Traps on unordered                      |

| *FTPCMP      | Trapping Predicate Compare Compares two arguments and affirms or disaffirms predicate Traps or unordered |

| LBSR         | Branch to Subroutine                                                                                     |

Table A-2. Abbreviations

C

0

\*These abbreviations represent the specific operations which are described in this appendix. See Appendix H for more definitions

# ABSOLUTE VALUE

C

0

| Mnemonic:                     | FAB                                                                                                                                             |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:                    | [arg2]-result                                                                                                                                   |

| Description:                  | Return absolute value of arg2 as the result.                                                                                                    |

| Opcode:                       | \$1E                                                                                                                                            |

| Precisions:                   | All. The result will have the same precision as arg2. The precision is<br>specified in bits 5-7 of the FPCB control byte.                       |

| Register                      |                                                                                                                                                 |

| Calling<br>Sequence:          | load X with address of result<br>load Y with address of arg2<br>load D with address of FPCB<br>LBSR FPREG (FPREG = ROM start + \$3D)<br>FCB FAB |

|                               | The result is automatically returned to user memory. This calling sequence is the same for all monadic calls.                                   |

| Stack<br>Calling<br>Sequence: | push arg2<br>push address of FPCB<br>LBSR FPSTAK (FPSTAK = ROM start + \$3F)<br>FCB FAB<br>pull result                                          |

|                               | Only the result is left on the stack after return from the subroutine. This                                                                     |

Only the result is left on the stack after return from the subroutine. This calling sequence is the same for all monadic calls.

# ADD

Mnemonic: FADD

6

Operation: arg1+arg2-result

Description: Add arg2 to arg1 and store the result.

Opcode: \$00

Precisions: All. Both arg1 and arg2 must be of the same precision. The result will also be the same precision. The precision is specified in bits 5-7 of the FPCB control byte.

Register

Calling

Sequence:

load X with the address of the result load Y with the address of arg2 load U with the address of arg1 load D with the address of the FPCB LBSR FPREG (FPREG = ROM start + \$3D) FCB FADD

The result is automatically returned to user memory. This calling sequence is the same for all dyadic calls.

Stack

Sequence:

push arg1 push arg2 push address of FPCB LBSR FPSTAK (FPSTAK = ROM start + \$3F) FCB FADD pull result

Only the result is left on the stack after the call. This calling sequence is the same for all dyadic calls.

# BINARY FLOATING TO DECIMAL STRING

Mnemonic: BINDEC

Operation: arg2-BCD string with k significant digits

Description: Convert a floating point argument in arg2 to an unpacked BCD string in the result. A parameter k is also passed to the routine to indicate the number of significant digits desired in the result (1≤k≤9 for single: 1≤k≤17 for double)

Opcode: SIC

Precisions: Single and double results are delivered to the accuracy required by the proposed IEEE standard. Extended results, however, are not necessarily more accurate than double and may take considerably more time to compute. The precision of arg2 is specified in bits 5-7 of the FPCB control byte. The output BCD string is a standard 26 byte BCD string of the form:

| 0  |                      | 5  |                       |   |

|----|----------------------|----|-----------------------|---|

| se | 4 Digit BCD Exponent | sf | 19 Digit BCD Fraction | P |

se = sign of the exponent. 00 = plus, \$0F = minus. sf = sign of the fraction. 00 = plus, \$0F = minus.

p = number of fraction digits to the right of the decimal point (one byte).

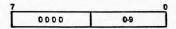

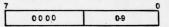

All BCD digits are unpacked and right justified in each byte:

| 0000 | 0-9 |  |  |

|------|-----|--|--|

Since some special floating point values have no obvious BCD equivalent, the sign of the exponent (se) is used to indicate these special cases:

se = 00 = regular positive number.

- = OF = regular negative number.

- = DC = NAN. The four digit BCD exponent contains the unpacked hex address that was in the NAN.

- = 0B = minus infinity. All remaining bytes of the BCD string are zero.

- = 0A = plus Infinity. All remaining bytes of the BCD string are zero.

Even though these special numbers can be created as output, they are not legal inputs to DECBIN.

Register Calling Sequence:

load X with address of result load Y with address of arg2 load U with k load D with address of FPCB LBSR FPREQ (FPREG = ROM start + \$3D) FCB BINDEC

The resultant BCD string is automatically returned to the user.

Stack Calling Sequence:

push arg2 push k push address of FPCB LBSR FPSTAK (FPSTAK = ROM start + \$3F) FCB BINDEC pull BCD string

# COMPARE

#### Mnemonic: FCMP, FTCMP, FPCMP, FTPCMP

Operation: arg1-arg2 (return condition code register or affirm/disaffirm a predicate)

Description: Compare arg1 with arg2. Both arg1 and arg2 may be of different precisions. Two basic types of compares are provided. One returns condition codes in the condition code register to the user to indicate the result of the comparison. The other is given a predicate (e.g., is arg1 equal to arg2?) and either affirms or disaffirms the predicate.

1) Condition code compares:

#### FCMP

Compare arg1 with arg2 and set the condition codes. Do not trap on unordered unless the trap on unordered bit (UNOR) is set in the trap enable byte of the FPCB.

#### FTCMP

Compare arg1 with arg2 and set the condition codes. Trap if the unordered conditions occur regardless of the state of the UNOR bit in the trap enable byte of the FPCB.

The intermediate result of any comparison can yield one of five possible results: ang 1 is > ang 2, ang 1 is < ang 2, ang 1 = ang 2, ang 1 + ang 2, ang 1 + ang 2, or g 1 + ang 2 (unordered). The unordered condition occurs when a comparison is made between a NAN and anything else or when infinity is compared to anything except itself in projective closure. This intermediate result is then used to set the condition code as follows:

| Result    | N | z | V | C |  |

|-----------|---|---|---|---|--|

| >         | 0 | 0 | 0 | 0 |  |

| <         | 1 | 0 | 0 | 0 |  |

| =         | 0 | 1 | 0 | 0 |  |

| unordered | 0 | 0 | 0 | 1 |  |

The remaining condition code register bits (E, F, H, and I) are unaffected by compare.

This allows the following signed branches to be taken immediately following the return from FCMP or FTCMP.

| Branch | Test for Branch                                          |

|--------|----------------------------------------------------------|

| (L)BGT | [not (N . V)] and (not Z) = 1                            |

| (L)BGE | not (N • V) = 1                                          |

| (L)BLT | not $(N \bullet V) = 0$                                  |

| (L)BLE | not (N . V) and (not Z) = 0                              |

| (L)BEQ | Z=1                                                      |

| (L)BNE | Z=0                                                      |

| (L)BCS | C=1                                                      |

|        | (L)BGT<br>(L)BGE<br>(L)BLT<br>(L)BLE<br>(L)BEQ<br>(L)BNE |

If FCMP and the unordered trap is disabled, a BCS should immediately follow the call and precede any of the other branches:

LBSR fpxxx FCB FCMP BCS unordered BGE tabel

Note that this implementation of compare conditions (as defined by the proposed IEEE standard) does not support the dichotomy principle normally associated with Integer compare. For example, BGE is not necessarily the inverse of BLT (the result may be unordered too). Compiler writers must take care not to switch the condition of a branch during code generation.

#### 2) Predicate Compares

#### FPCMP

Compare arg1 with arg2. Either affirm or disaffirm an Input predicate. Do not trap on unordered unless the UNOR bit is set in the trap enable byte of the FPCB. For register calls the Z-bit in the condition code register is set to 1 for affirm (true) and set to 0 for disaffirm (false). For stack calls a byte of zeros is pushed on top of the stack for true and a byte of ones (\$FF) is pushed for false.

#### FTPCMP

Compare arg1 with arg2. Either affirm or disaffirm an input predicate. Trap If the unordered condition occurs regardless of the state of the UNOR bit in the trap enable byte of the FPCB. For register calls the Z-bit in the condition code register is set to 1 for affirm (true) and set to 0 for disaffirm (false). For stack calls a byte of zeros is pushed on top of the stack for true and a byte of ones (SFP is pushed for false.

Unordered conditions occur when a comparison is made between a NAN and anything else or when infinity is compared to anything except itself in projective closure.

The predicate to be affirmed or disaffirmed is passed to the compare in the parameter word:

| 15  |   | 11 |   | edica |   |   |   |      | 4 3 | 2    | 0 |

|-----|---|----|---|-------|---|---|---|------|-----|------|---|

| 000 | * | >  | = | <     | U | Τ | 0 | arg1 | 0   | arg2 |   |

The predicates are >,  $\times$ , <, and unordered, or a reasonable combination of these (e.g., > =). The intermediate result of a predicate compare is either >, =, <, or unordered. The table below gives the predicate affirmed or disalfirmed for each possible intermediate result.

Intermediate Result less than equal greater than unordered **Predicates Affirmed**

< 5 . = 5 2 > 2 . unordered

Intermediate Result less than equal greater than unordered **Predicates Disaffirmed**

- $z \ge unordered$  $z \ge unordered \neq$  $z \le unordered$

- < = > > < >

The result returned for affirmed is a zero byte and for disaffirmed it is a - 1 or SFF byte for a stack call. For a register call, Z = 1 if the predicate is affirmed.

Opcodes: FCMP=\$BA FTCMP=\$CC FPCMP=\$BE FTPCMP=\$D0

Precisions: Since the compares allow arg1 and arg2 to be of different precisions, a parameter word must be passed on each call to any compare. The format of the parameter word is:

| 15  |   | 11 | Pre | edica | tes | 8 7 | 6 4  | 3 | 2 1  | 0 |

|-----|---|----|-----|-------|-----|-----|------|---|------|---|

| 000 | # | >  | =   | <     | J   | 0   | arg1 | 0 | arg2 |   |

Where arg1 or arg2 is defined:

| Single                        |

|-------------------------------|

| Double                        |

| Extended                      |

| Unused (defaults to extended) |

| Unused (defaults to extended) |

| Undefined                     |

|                               |

Since the parameter word specifies both arguments of the compare, bits 5-7 of the control byte of the FPCB do not affect the compare instructions.

Register Calling Sequence:

C

load X with the parameter word load Y with address of arg2 load U with address of arg1 load D with address of FPCB LBSR FPREG (FPREG = ROM start + \$3D) FCB < Opcode >

The result is returned in the condition code register, it is either a setting of the condition code register (condition code call) or the Z bit is set to 1 for affirm and Z = 0 for disaffirm (predicate calls).

Stack Calling Sequence:

push arg1 push arg2 push parameter word push address of the FPCB LBSR FPREG (FPREG = ROM start + \$3F) FCB < Opcode> pull result

If the compare is a condition code compare, no result is delivered on the stack — only the condition codes are returned in the condition code register. If the compare is a predicate compare, a 1-byte result is returned on top of the stack. The result = 0 for affirmed and -1 (\$FF) for disaffirmed.

## DECIMAL STRING TO BINARY FLOATING POINT

# Source Form: DECBIN Operation: BCD string – floating point result Description: Convert a standard BCD string into a binary floating point result. The value "p" in the standard decimal string indicates the number of digits of the fraction that are to the right of the decimal point.

Opcode: \$22

Precisions: The precision of the result is defined by bits 5-7 of the FPCB control byte. The input BCD string is a standard 26 byte BCD string of the form:

| 0  |                      | 5  | 6 24                  |   |

|----|----------------------|----|-----------------------|---|

| se | 4 Digit BCD Exponent | sf | 19 Digit BCD Fraction | P |

se = sign of the exponent.00 = plus, \$0F = minus (one byte). sf = sign of the fraction.00 = plus, \$0F = minus (one byte). p = number of fraction digits to the right of the decimal point (one byte).

All BCD digits are unpacked and right justified in each byte:

The byte ordering of the fraction and exponent is consistent with all Motorola processors in that the most significant BCD digit is in the lowest memory address.

Register Calling

Sequence: load X with the address of result load U with the address of the BCD input string load D with the address of the FPCB LBSR FPREG (FPREG = ROM start + \$3D) FCB DECBIN

The result is automatically returned to the user.

Stack

Calling

Sequence:

push the BCD string push address of the FPCB LBSR FPSTAK (FPSTAK = ROM start + \$3F) FCB DECBIN pull floating point result

## DIVIDE

0

C

6

| Mnemonic:        | FDIV                                                                                                                                                                                                    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:       | arg1/arg2-result                                                                                                                                                                                        |

| Description:     | Divide arg1 by arg2 and store the result.                                                                                                                                                               |

| Opcode:          | \$06                                                                                                                                                                                                    |

| Precisions:      | Both arg1 and arg2 must be of the same precision. The result will also be<br>the same precision. The precision is specified in bits 5-7 of the FPCB con-<br>trol byte.                                  |

| Register         |                                                                                                                                                                                                         |

| Sequence:        | load X with the address of the result<br>load Y with the address of arg2<br>load U with the address of arg1<br>load D with the address of the FPCB<br>LBSR FPREG (FPREG = ROM start + \$3D)<br>FCB FDIV |

|                  | The result is automatically returned to user memory. The calling sequence is the same for all dyadic calls.                                                                                             |

| Stack<br>Calling |                                                                                                                                                                                                         |

| Sequence:        | push arg1<br>push arg2<br>push address of FPCB<br>LBSR FPSTAK (FPSTAK = ROM start + \$3F)<br>FCB FDIV<br>pull result<br>Only the result is left on the stack after the call. This calling sequence is   |

|                  | the same for all dyadic calls.                                                                                                                                                                          |

## FIX

0

| Mnemonic:           | FFIXS, FFIXD                                                                                                                                                                               |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:          | arg2-binary integer result                                                                                                                                                                 |

| Description:        | Converts arg2 from a floating point number into a 16- or 32-bit binary in-<br>teger. If arg2 is infinity, then the integer returned is the largest or smallest<br>twos complement integer. |

| Opcode:             | FFIXS = \$16 (16-bit integer)<br>FFIXD = \$18 (32-bit integer)                                                                                                                             |

| Precisions:         | Same as absolute value except that the result will be a 16- or 32-bit integer as specified by the opcode.                                                                                  |

| Register<br>Calling |                                                                                                                                                                                            |

| Sequence:           | load X with the address of the result<br>load Y with the address of arg2<br>load D with the address of the FPCB<br>LBSR FPREG (FPREG = ROM start + \$3D)<br>FCB FFIXS or FFIXD             |

|                     | The result is automatically returned to user memory. The calling sequence is the same for all monadic calls.                                                                               |

| Stack<br>Calling    |                                                                                                                                                                                            |

| Sequence:           | push arg2<br>push address of FPCB<br>LBSR FPSTAK (FPSTAK = ROM start + \$3F)<br>FCB FFIXS or FFIXD<br>pull result                                                                          |

|                     | Only the result is left on the stack after return from the subroutine This                                                                                                                 |

Only the result is left on the stack after return from the subroutine. This calling sequence is the same for all monadic calls.

### FLOAT

Mnemonic: FFLTS, FFLTD

Operation: Binary Integery arg2-floating point result

Description: Converts a 16- or 32-bit integer into a floating point result.

Opcode: FFLTS = \$24 (16-bit binary integer) FFLTD = \$26 (32-bit binary integer)

Precisions: All. The size of the binary integer is specified in the opcode. The precision is specified in bits 5-7 of the FPCB control byte.

Register

Calling

Sequence: load X with the address of the result load Y with the address of arg2 load D with the address of the FPCB LBSR FPREG (FPRET = ROM start + \$3D) FCB FFLTS or FFLTD

The result is automatically returned to user memory. The calling sequence is the same for all monadic calls.

#### Stack

Calling

Sequence:

push arg2 push address of FPCB LBSR FPSTAK (FPSTAK = ROM start + \$3F) FCB FFLTS or FFLTD pull result

Only the result is left on the stack after return from the subroutine. This calling sequence is the same for all monadic calls.

## INTEGER PART

(0

6

| Mnemonic:                        | FINT                                                                                                                                                                                                                                                                                    |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation:                       | Integer part (arg2)-floating point result                                                                                                                                                                                                                                               |

| Description:                     | The floating point argument in arg2 is converted to its floating point integer part. This differs from FIX which returns a binary integer. Integer part returns a floating point number. For example, the integer part of 3.14159 is 3.00000 if the rounding mode is round to nearest.  |

| Opcode:                          | \$14                                                                                                                                                                                                                                                                                    |

| Precisions:                      | All. The result will have the same precision as arg2. The precision is specified in bits 5-7 of the FPCB control byte.                                                                                                                                                                  |

| Register<br>Calling<br>Sequence: | load X with the address of the result<br>load Y with the address of arg2<br>load D with the address of the FPCB<br>LBSR FPREG (FPREG = ROM start + \$3D)<br>FCB FINT<br>The result is automatically returned to user memory. The calling sequence<br>is the same for all monadic calls. |

| Stack<br>Calling<br>Sequence:    | push arg2<br>push address of FPCB<br>LBSR FPSTAK (FPSTAK = ROM start + \$3F)<br>FCB FINT<br>pull result<br>Only the result is left on the stack after return from the subroutine. This<br>calling sequence is the same for all monadic calls.                                           |

### MOVE

Mnemonic: FMOV

Operation: arg2-result

Description: For register calls, the move instruction moves arg2 to the result. Since moves allow mixed precisions, they can be used to convert a number from one precision to another during the move. For stack calls, the move is essentially a "convert precision of stack top" operation.

Opcode: \$9A

Precisions: The move allows arg2 and the result to be of different precisions. In order to specify the two precisions, a parameter word must be passed on each call to move. The form of the parameter word is:

| 15       | 8 6 |      | 4 2 | 0      |

|----------|-----|------|-----|--------|

| 00000000 | 0   | arg2 | 0   | result |

Where arg2 (source) or result (destination) is defined:

| 000     | Single                   |

|---------|--------------------------|

| 001     | Double                   |

| 010     | Extended                 |

| 011     | Extended round to single |

| 100     | Extended round to double |

| 101-111 | lliegal                  |

Since the parameter word specifies both arguments of the move, bits 5-7 of the FPCB control byte do not affect the move operation.

Register Calling

Sequence: